# TrustZone® Address Space Controller (TZC-380)

Revision: r0p0

**Technical Reference Manual**

### TrustZone Address Space Controller (TZC-380) Technical Reference Manual

Copyright © 2008, 2010 ARM Limited. All rights reserved.

#### **Release Information**

The Change history table lists the changes made to this book.

#### Change history

| Date              | Issue | Confidentiality  | Change                  |

|-------------------|-------|------------------|-------------------------|

| 10 September 2008 | A     | Confidential     | First release for r0p0  |

| 19 March 2010     | В     | Non-Confidential | Second release for r0p0 |

#### **Proprietary Notice**

Words and logos marked with  $^{\circ}$  or  $^{\bowtie}$  are registered trademarks or trademarks of ARM $^{\circ}$  in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

Unrestricted Access is an ARM internal classification.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

### Contents

## **TrustZone Address Space Controller (TZC-380) Technical Reference Manual**

|            | Prefa | Preface                              |     |  |

|------------|-------|--------------------------------------|-----|--|

|            |       | About this book                      | х   |  |

|            |       | Feedback                             |     |  |

| Chapter 1  | Intro | oduction                             |     |  |

| •          | 1.1   | About the TZASC                      | 1-2 |  |

|            | 1.2   | Product revisions                    |     |  |

| Chapter 2  | Fund  | ctional Description                  |     |  |

| -          | 2.1   | Functional interfaces                | 2-2 |  |

|            | 2.2   | Functional operation                 |     |  |

|            | 2.3   | Constraints of use                   |     |  |

| Chapter 3  | Prog  | grammers Model                       |     |  |

| •          | 3.1   | About the programmers model          | 3-2 |  |

|            | 3.2   | Register descriptions                |     |  |

| Chapter 4  | Proc  | grammers Model for Test              |     |  |

| •          | 4.1   | About the programmers model for test | 4-2 |  |

|            | 4.2   | Integration test registers           | 4-3 |  |

| Appendix A | Sign  | nal Descriptions                     |     |  |

| • •        | A.1   | Clock and reset signals              | A-2 |  |

|            | A.2   | AXI signals                          |     |  |

|            | A.3   | APB signals                          |     |  |

|            | A.4   | Miscellaneous signals                |     |  |

|            |       | 3                                    |     |  |

Appendix B Revisions

Glossary

### List of Tables

## **TrustZone Address Space Controller (TZC-380) Technical Reference Manual**

|            | Change history                                                    | i                |

|------------|-------------------------------------------------------------------|------------------|

| Table 2-1  | AXI slave interface attributes                                    |                  |

| Table 2-2  | AXI master interface attributes                                   |                  |

| Table 2-3  | Region security permissions when security inversion is disabled   | 2-9              |

| Table 2-4  | Region security permissions when security inversion is enabled    | 2-9              |

| Table 2-5  | Typical example of memory map along with the register programming | 2-10             |

| Table 3-1  | Register summary                                                  |                  |

| Table 3-2  | configuration Register bit assignments                            | 3-7              |

| Table 3-3  | action Register bit assignments                                   | 3-8              |

| Table 3-4  | lockdown_range Register bit assignments                           | 3-9              |

| Table 3-5  | lockdown_select Register bit assignments                          | 3-10             |

| Table 3-6  | int_status Register bit assignments                               | 3-1 <sup>-</sup> |

| Table 3-7  | fail_address_low Register bit assignments                         | 3-12             |

| Table 3-8  | fail_address_high Register bit assignments                        | 3-13             |

| Table 3-9  | fail_control Register bit assignments                             | 3-14             |

| Table 3-10 | fail_id Register bit assignments                                  |                  |

| Table 3-11 | speculation_control Register bit assignments                      | 3-16             |

| Table 3-12 | security_inversion_en Register bit assignments                    | 3-17             |

| Table 3-13 | region_setup_low_ <n> Register bit assignments</n>                |                  |

| Table 3-14 | region_setup_high_ <n> Register bit assignments</n>               | 3-19             |

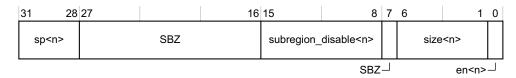

| Table 3-15 | region_attributes_ <n> Register bit assignments</n>               | 3-20             |

| Table 3-16 | Region size                                                       | 3-2              |

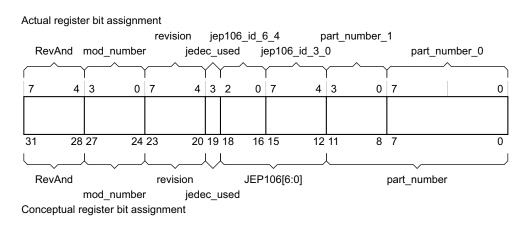

| Table 3-17 | periph_id_[3:0] Register bit assignments                          | 3-23             |

| Table 3-18 | periph_id_0 Register bit assignments                              |                  |

| Table 3-19 | periph_id_1 Register bit assignments                              | 3-24             |

| Table 3-20 | periph_id_2 Register bit assignments                              | 3-24             |

| Table 3-21 | periph_id_3 Register bit assignments                              | 3-25             |

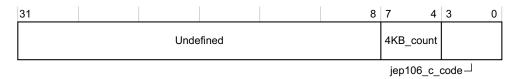

| Table 3-22 | periph_id_4 Register bit assignments        | 3-25 |

|------------|---------------------------------------------|------|

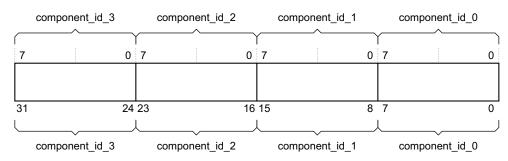

| Table 3-23 | component_id Register bit assignments       |      |

| Table 3-24 | component_id_0 Register bit assignments     | 3-27 |

| Table 3-25 | component_id_1 Register bit assignments     | 3-27 |

| Table 3-26 | component_id_2 Register bit assignments     | 3-27 |

| Table 3-27 | component_id_3 Register bit assignments     | 3-27 |

| Table 4-1  | Test register summary                       |      |

| Table 4-2  | itcrg Register bit assignments              |      |

| Table 4-3  | itip Register bit assignments               | 4-5  |

| Table 4-4  | itop Register bit assignments               | 4-6  |

| Table A-1  | Clock and reset signals                     | A-2  |

| Table A-2  | AXI-AW signals for the AXI slave interface  | A-3  |

| Table A-3  | AXI-W signals for the AXI slave interface   | A-4  |

| Table A-4  | AXI-B signals for the AXI slave interface   | A-4  |

| Table A-5  | AXI-AR signals for the AXI slave interface  | A-4  |

| Table A-6  | AXI-R signals for the AXI slave interface   | A-5  |

| Table A-7  | AXI-AW signals for the AXI master interface | A-6  |

| Table A-8  | AXI-W signals for the AXI master interface  | A-6  |

| Table A-9  | AXI-B signals for the AXI master interface  | A-7  |

| Table A-10 | AXI-AR signals for the AXI master interface | A-7  |

| Table A-11 | AXI-R signals for the AXI master interface  | A-8  |

| Table A-12 | APB slave interface signals                 | A-9  |

| Table A-13 | secure_boot_lock signal                     | A-10 |

| Table A-14 | tzasc_int signal                            | A-10 |

| Table B-1  | Differences between issue A and issue B     | R-1  |

### List of Figures

## **TrustZone Address Space Controller (TZC-380) Technical Reference Manual**

|             | Key to timing diagram conventions                   | X    |

|-------------|-----------------------------------------------------|------|

| Figure 1-1  | Interfaces on the TZASC                             | 1-2  |

| Figure 1-2  | Example system                                      | 1-2  |

| Figure 2-1  | Miscellaneous signals                               | 2-3  |

| Figure 2-2  | Functional operation of TZASC                       | 2-5  |

| Figure 2-3  | Region priority                                     | 2-6  |

| Figure 2-4  | Subregion example                                   | 2-7  |

| Figure 2-5  | Subregion disable example                           | 2-8  |

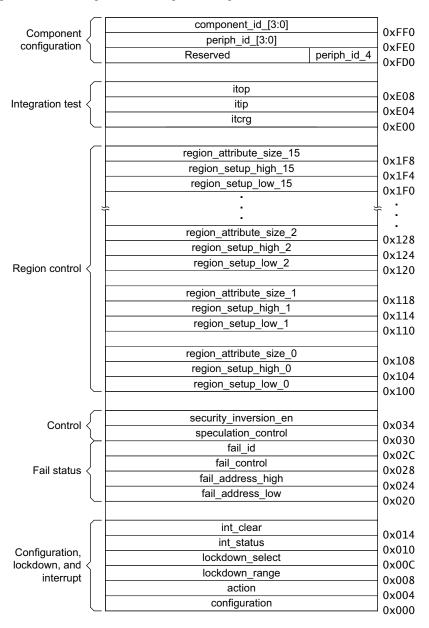

| Figure 3-1  | Register map                                        | 3-3  |

| Figure 3-2  | configuration Register bit assignments              | 3-6  |

| Figure 3-3  | action Register bit assignments                     | 3-8  |

| Figure 3-4  | lockdown_range Register bit assignments             | 3-9  |

| Figure 3-5  | lockdown_select Register bit assignments            | 3-10 |

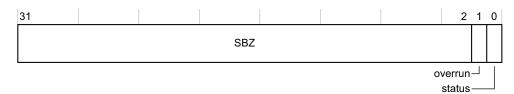

| Figure 3-6  | int_status Register bit assignments                 | 3-11 |

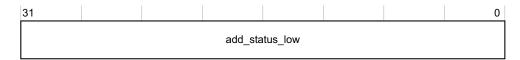

| Figure 3-7  | fail_address_low Register bit assignments           | 3-12 |

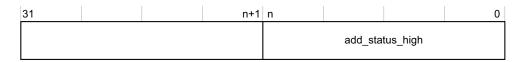

| Figure 3-8  | fail_address_high Register bit assignments          | 3-13 |

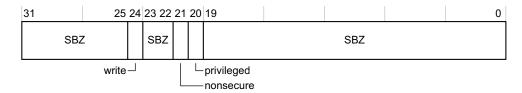

| Figure 3-9  | fail_control Register bit assignments               | 3-14 |

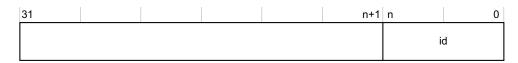

| Figure 3-10 | fail_id Register bit assignments                    | 3-15 |

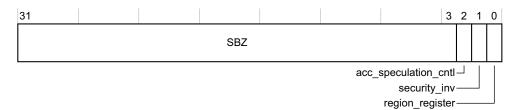

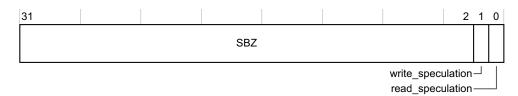

| Figure 3-11 | speculation_control Register bit assignments        | 3-16 |

| Figure 3-12 | security_inversion_en Register bit assignments      | 3-17 |

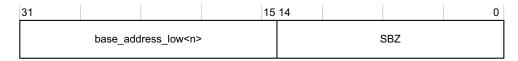

| Figure 3-13 | region_setup_low_ <n> Register bit assignments</n>  | 3-18 |

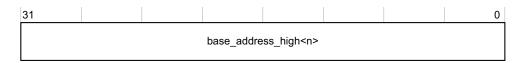

| Figure 3-14 | region_setup_high_ <n> Register bit assignments</n> | 3-19 |

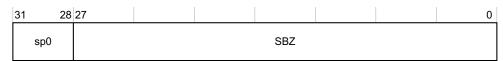

| Figure 3-15 | region_attributes_ <n> Register bit assignments</n> | 3-20 |

| Figure 3-16 | periph_id_[3:0] Register bit assignments            | 3-23 |

| Figure 3-17 | periph_id_4 Register bit assignments                | 3-25 |

| Figure 3-18 | Component ID Register bit assignments               | 3-26 |

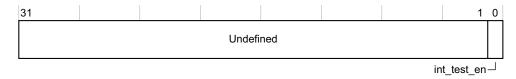

| Figure 4-1  | itcrg Register bit assignments                      | 4-4  |

| Figure 4-2 | itip Register bit assignments | 4-5 |

|------------|-------------------------------|-----|

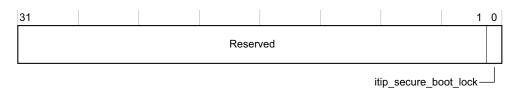

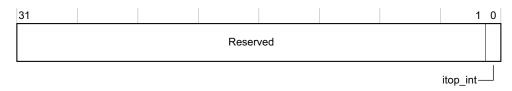

| Figure 4-3 | itop Register bit assignments | 4-6 |

### **Preface**

This preface introduces the *TrustZone Address Space Controller (TZC-380) Technical Reference Manual* (TRM). It contains the following sections:

- About this book on page x

- Feedback on page xiv.

#### About this book

This is the TRM for the TrustZone Address Space Controller (TZC-380).

#### **Product revision status**

The rnpn identifier indicates the revision status of the product described in this book, where:

**rn** Identifies the major revision of the product.

**pn** Identifies the minor revision or modification status of the product.

#### Intended audience

This book is written for system designers, system integrators, and programmers who are designing or programming a *System-on-Chip* (SoC) that uses the TZASC.

#### Using this book

This book is organized into the following chapters:

#### Chapter 1 Introduction

Read this for an introduction to the TZASC and its features.

#### Chapter 2 Functional Description

Read this for a description of the major interfaces and the functional operation of the TZASC.

#### Chapter 3 Programmers Model

Read this for a description of the memory map and registers.

#### Chapter 4 Programmers Model for Test

Read this for a description of the test registers.

#### Appendix A Signal Descriptions

Read this for a description of the input and output signals.

#### Appendix B Revisions

Read this for a description of the technical differences between consecutive revisions of this book.

**Glossary** Read the glossary for definitions of terms used in this book.

#### Conventions

Conventions that this book can use are described in:

- Typographical

- Timing diagrams on page xi

- Signals on page xi.

#### **Typographical**

The typographical conventions are:

*italic* Highlights important notes, introduces special terminology, denotes

internal cross-references, and citations.

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.   |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                             |  |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name. |  |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                           |  |

| monospace bold    | Denotes language keywords when used outside example code.                                                                               |  |

| < and >           | Enclose replaceable terms for assembler syntax where they appear in code or code fragments. For example:                                |  |

#### **Timing diagrams**

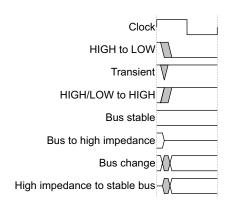

The figure named Key to timing diagram conventions explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

MRC p15,  $\emptyset$  <Rd>, <CRn>, <CRm>, <Opcode\_2>

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Key to timing diagram conventions

#### **Signals**

| The signal conventi | ons are:                                                                                                                                                               |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal level        | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:  HIGH for active-HIGH signals  LOW for active-LOW signals. |  |

| Prefix a            | Denotes global Advanced eXtensible Interface (AXI) signals.                                                                                                            |  |

| Prefix ar           | Denotes AXI read address channel signals.                                                                                                                              |  |

| Prefix aw           | Denotes AXI write address channel signals.                                                                                                                             |  |

| Prefix b            | Denotes AXI write response channel signals.                                                                                                                            |  |

Prefix p Denotes Advanced Peripheral Bus (APB) signals.

Prefix n Denotes an active-LOW signal.

Prefix r Denotes AXI read data channel signals.

**Prefix w** Denotes AXI write data channel signals.

#### **Additional reading**

This section lists publications by ARM and by third parties.

See http://infocenter.arm.com for access to ARM documentation.

#### **ARM** publications

This book contains information that is specific to the TZASC. See the following documents for other relevant information:

- TrustZone Address Space Controller (TZC-380) Implementation Guide (ARM DII 0249)

- TrustZone Address Space Controller (TZC-380) Integration Manual (ARM DII 0250)

- TrustZone Address Space Controller (TZC-380) Supplement to AMBA Designer (ADR-301) User Guide (ARM DSU 0014)

- AMBA Designer (ADR-301) User Guide (ARM DUI 0333)

- AMBA AXI Protocol Specification (ARM IHI 0022)

- AMBA 3 APB Protocol Specification (ARM IHI 0024)

- TrustZone Address Space Controller (TZC-380) Release Note

- *AMBA Specification (Rev 2.0)* (ARM IHI 0011).

#### Other publications

This section lists relevant documents published by third parties:

• JEDEC Solid State Technology Association, *JEP106, Standard Manufacturer's Identification Code*, obtainable at http://www.jedec.org.

#### **Feedback**

ARM welcomes feedback on this product and its documentation.

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- the title

- the number, ARM DDI 0431B

- the page numbers to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

## Chapter 1 **Introduction**

This chapter introduces the *TrustZone Address Space Controller (TZC-380)*. It contains the following sections:

- *About the TZASC* on page 1-2

- *Product revisions* on page 1-4.

#### 1.1 About the TZASC

The TZASC is an *Advanced Microcontroller Bus Architecture* (AMBA) compliant *System-on-Chip* (SoC) peripheral. It is a high-performance, area-optimized address space controller with on-chip AMBA bus interfaces that conform to the AMBA *Advanced eXtensible Interface* (AXI) protocol and the AMBA *Advanced Peripheral Bus* (APB) protocol.

You can configure the TZASC to provide the optimum security address region control functions required for your intended application. See *Features of the TZASC* for a summary of the configurable features supported.

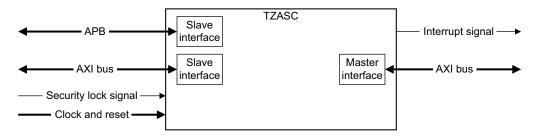

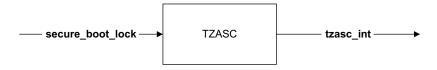

Figure 1-1 shows the interfaces that are available on the TZASC.

Figure 1-1 Interfaces on the TZASC

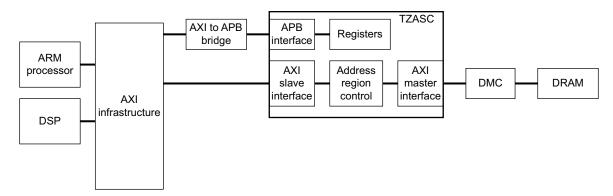

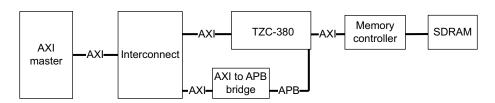

Figure 1-2 shows the TZASC in an example system.

Figure 1-2 Example system

The TZASC example system contains:

- an AXI to APB bridge restricting APB traffic to the TZASC to secure only

- a TZASC

- AXI bus masters:

- an ARM processor

- a Digital Signal Processor (DSP).

- AXI infrastructure component

- a Dynamic Memory Controller (DMC).

#### 1.1.1 Features of the TZASC

The TZASC provides the following features:

- enables you to program security access permissions for each address region

- permits the transfer of data between master and slave only if the security status of the AXI transaction matches the security settings of the memory region it addresses

prevents write access to various registers after assertion of **secure\_boot\_lock**.

#### You can configure the:

- AXI address bus width to be 32-bit to 64-bit inclusive

- AXI data bus width to be 32-bit, 64-bit, 128-bit, or 256-bit

- AXI ID tag width to be 1-bit to 24-bit inclusive

- AXI **USER** bus width to be 0-bit to 32-bit inclusive

- number of address regions to be:

- 2 regions

- 4 regions

- 8 regions

- 16 regions.

- APB protocol version to be AMBA 2 or AMBA 3

- transaction tracking queue depth to be 1-16 inclusive

- timing close options:

- no pipeline stages

- forward direction timing isolation on slave interface and master interface AXI ports

- complete timing isolation on slave interface and master interface AXI ports.

#### 1.2 Product revisions

This section describes the differences in functionality between product revisions:

**r0p0** First release.

## Chapter 2 **Functional Description**

This chapter describes the TZASC operation. It contains the following sections:

- Functional interfaces on page 2-2

- Functional operation on page 2-5

- *Constraints of use* on page 2-14.

#### 2.1 Functional interfaces

The main interfaces of the TZASC are:

- AXI bus interfaces

- *APB slave interface* on page 2-3

- *Miscellaneous signals* on page 2-3

- *Clock and reset* on page 2-4.

#### 2.1.1 AXI bus interfaces

The TZASC provides the following AXI bus interfaces:

- AXI slave interface

- *AXI master interface* on page 2-3.

Each AXI bus interface consists of the following AXI channels:

- Write Address (AW)

- Write Data (W)

- Write Response (B)

- Read Address (AR)

- Read Data (R).

See the AMBA AXI Protocol v1.0 Specification for information about the AXI protocol.

#### **AXI slave interface**

Table 2-1 shows the AXI slave interface attributes and their values.

Table 2-1 AXI slave interface attributes

| Attribute <sup>a</sup>         | Value                                                                                                                                                                                                       |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Read acceptance capability     | Equals the configurable transaction tracker queue depth. If register slices are enabled on AR channel, the read acceptance capability is configurable transaction tracker queue depth plus one.             |  |

| Write acceptance capability    | Equals the configurable transaction tracker queue depth. If register slices are enabled on AW channel, the write acceptance capability is configurable transaction tracker queue depth plus one.            |  |

| Combined acceptance capability | Equals the configurable transaction tracker queue depth. If register slices are enabled on AR and AW channels, the combined acceptance capability is configurable transaction tracker queue depth plus two. |  |

| Write interleave depth         | 1                                                                                                                                                                                                           |  |

| Read data reordering depth     | Equal to zero. The TZASC does not re-order read data. However the TZASC supports the re-ordering depth of the downstream slave.                                                                             |  |

a. See Glossary for a description of these AXI attributes.

#### **AXI** master interface

Table 2-2 shows the AXI master interface attributes and their values.

Table 2-2 AXI master interface attributes

| Attribute <sup>a</sup>      | Value                                                            |

|-----------------------------|------------------------------------------------------------------|

| Combined issuing capability | Equals the transaction tracking queue depth that is configurable |

| Write issuing capability    | Equals the transaction tracking queue depth that is configurable |

| Read issuing capability     | Equals the transaction tracking queue depth that is configurable |

a. See Glossary for a description of these AXI attributes.

#### 2.1.2 APB slave interface

The APB slave interfaces provide access to the TZASC registers that enables you to program the system configuration parameters and obtain status information. See Chapter 3 *Programmers Model* for more information.

The APB slave interface must only be accessible to processors in Secure state, otherwise it can compromise the security of the system.

You can configure the TZASC to support either the:

- AMBA 2 APB protocol

- AMBA 3 APB protocol.

See the AMBA 2 APB Protocol v1.0 Specification or AMBA 3 APB Protocol v1.0 Specification for more information.

If you configure the TZASC to support the AMBA 2 APB protocol, it provides all the signals, except **pready** and **pslverr**.

#### 2.1.3 Miscellaneous signals

There are two miscellaneous signals:

- secure\_boot\_lock

- tzasc int.

Figure 2-1 shows the miscellaneous signals that the TZASC provides.

Figure 2-1 Miscellaneous signals

Asserting **secure\_boot\_lock** enhances the security of the TZASC. See *Preventing writes to registers and using secure boot lock* on page 2-12.

You can program the TZASC to assert **tzasc\_int** when it denies an AXI master access to a region. See *Denied AXI transactions* on page 2-11.

#### 2.1.4 Clock and reset

This section describes:

- Clock

- Reset

- pclken.

#### Clock

All configurations of the TZASC use a single clock input, **aclk**. See *Clock and reset signals* on page A-2.

#### Reset

The TZASC provides a single reset input, **aresetn**. See *Clock and reset signals* on page A-2.

#### pclken

Clock enable signal that enables the APB slave interface to operate at either:

- the aclk frequency

- a divided integer multiple of **aclk** that is synchronous to **aclk**.

| Note                                                                                          |

|-----------------------------------------------------------------------------------------------|

| If you do not use pclken, you must tie it HIGH. This results in the APB slave interface being |

| clocked directly by aclk.                                                                     |

#### 2.2 Functional operation

TZASC is a systems IP that performs security checks on AXI accesses to memory, or off-chip peripheral. This supports configurable number of regions. Each region is programmable for size, base address, enable, and security parameters. Using the **secure\_boot\_lock**, the programmers view can be locked to prevent erroneous writes. See *Preventing writes to registers and using secure\_boot\_lock* on page 2-12. The IP provides programmability in reporting faults using AXI response channel, and interrupt.

Figure 2-2 Functional operation of TZASC

The following sections describe:

- Regions

- *Priority* on page 2-6

- Subregions on page 2-6

- *Subregion disable* on page 2-7

- Region security permissions on page 2-8

- Denied AXI transactions on page 2-11

- Speculative accesses on page 2-12

- Preventing writes to registers and using secure boot lock on page 2-12

- Using locked transaction sequences on page 2-13

- *Using exclusive accesses* on page 2-13.

The *TrustZone Address Space Controller (TZC-380) Supplement to AMBA Designer (ADR-301) User Guide* provides information about how to configure the controller.

#### 2.2.1 Regions

A region is a contiguous area of address space. The TZASC provides each region with a programmable security permissions field. The security permissions value is used to enable the TZASC to either accept or deny a transaction access to that region. The transactions **arprots[2:0]** or **awprots[2:0]** signals are used to determine the security settings of that transaction.

The TZASC always provides two regions, region 0 and region 1, and you can configure it to provide additional regions. With the exception of region 0, the TZASC enables you to program the following operating parameters for each region:

- Region enable.

- Security permissions.

- Base address.

- Size. The minimum address size of a region is 32KB.

- Subregion disable. See *Subregions* on page 2-6.

| Note |  |

|------|--|

|      |  |

Region 0 is known as the background region because it occupies the total memory space. You can program the security permissions of region 0, but the following parameters are fixed:

Base address 0x0

Size The AXI\_ADDRESS\_MSB configuration parameter controls the address range

of the TZASC, and therefore the region size.

**Subregion disable** This feature is not available for region 0.

#### 2.2.2 Priority

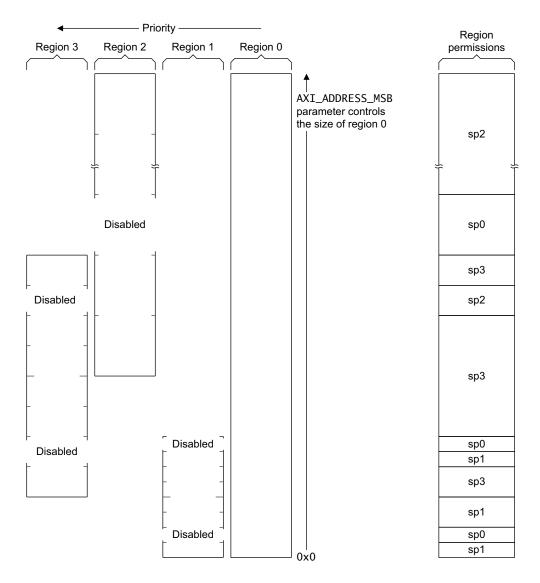

The priority of a region is fixed and is determined by the region number. Figure 2-3 shows how the priority of a region increases with the region number.

Figure 2-3 Region priority

When a transaction is received, its address is checked for a match with all the configured regions in turn. The order in which the regions are checked is determined by the priority level, the highest priority level is first. The first region that matches the transaction address match is used as the matching region. The matching regions security permission determines whether the transaction is permitted.

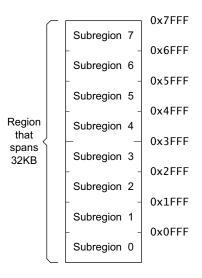

#### 2.2.3 Subregions

The TZASC divides each region into eight equal-sized, non-overlapping subregions. Figure 2-4 on page 2-7 shows the subregions for an example region that is programmed to occupy an address span of 32KB.

Figure 2-4 Subregion example

#### 2.2.4 Subregion disable

With the exception of region 0, you can program the TZASC to disable any or all of the eight subregions that comprise a region. When a subregion is disabled, the security permissions for its address range are provided by the next highest priority region that overlaps the address range.

#### Example 2-1 Example configuration for subregion disable

Figure 2-5 on page 2-8 shows an example configuration that supports four regions, where:

- region 2 and region 3 are partially overlapped

- region 1 and region 3 are partially overlapped

- region 0 is overlapped with all regions.

With some subregions of region 1, region 2, and region 3 are disabled, and the resulting region permissions of the entire address space is shown in the Figure 2-5 on page 2-8.

Figure 2-5 Subregion disable example

\_\_\_\_\_Note \_\_\_\_\_

In Figure 2-5:

- all subregions are enabled unless otherwise stated

- spn represents the region permissions of region n.

#### 2.2.5 Region security permissions

The TZASC enables you to program the security access permissions for any region that it is configured. A region is assigned a security permissions field, sp<n>, in its region\_attributes\_<n> Register that enables you to have complete control of the permissions for that region. See Chapter 4 *Programmers Model for Test*.

#### **Security inversion**

There are two modes of operation for the region security permissions, with or without security inversion.

Yes

No

Yes

By default, if you program a region to support non-secure accesses, the TZASC ensures that region must also support secure accesses. For example, if you program the region permissions for region 3 to be non-secure read only, the TZASC permits access to region 3 for secure reads and non-secure reads.

If you require that some regions are not accessible to masters in Secure state, but are accessible in Non-secure state, then you must enable security inversion.

See *Region security permissions* on page 2-8 and *Security Inversion Enable Register* on page 3-17 for more information.

#### Programming security permissions when security inversion is disabled

By default, security inversion is disabled and therefore the TZASC only permits you to program certain combinations of security permissions. These combinations ensure that a master in Secure state is not denied access to a region that is programmed to only accept non-secure accesses. Table 2-3 shows the possible security permissions when security inversion is disabled.

sp<n> field controls if the TZASC permits access for the following AXI transactions

Table 2-3 Region security permissions when security inversion is disabled

#### sp<n> fielda Secure read Secure write Non-secure read Non-secure write b0000 No No No No b0100 No Yes No No b0001, b0101 No No Yes Yes b1000 No Yes No No b0010, b1010 Yes No Yes No b1100 Yes Yes No No

Yes

Yes

Yes

Yes

Yes

Yes

#### Programming security permissions when security inversion is enabled

If you enable security inversion, the TZASC permits you to program any combination of security permissions as Table 2-4 shows.

sp<n> field controls if the TZASC permits access for the following AXI transactions

Table 2-4 Region security permissions when security inversion is enabled

No

Yes

Yes

| sp <n> field<sup>a</sup></n> | Secure read | Secure write | Non-secure read | Non-secure write |

|------------------------------|-------------|--------------|-----------------|------------------|

| b0000                        | No          | No           | No              | No               |

| b0001                        | No          | No           | No              | Yes              |

| b0010                        | No          | No           | Yes             | No               |

| b0011                        | No          | No           | Yes             | Yes              |

b1001, b1101

b0110, b1110

b0011, b0111, b1011, b1111

a. See *Region Attributes <n> Register* on page 3-20 for programming information.

Table 2-4 Region security permissions when security inversion is enabled (continued)

#### sp<n> field controls if the TZASC permits access for the following AXI transactions

| sp <n> fielda</n> | Secure read | Secure write | Non-secure read | Non-secure write |

|-------------------|-------------|--------------|-----------------|------------------|

| b0100             | No          | Yes          | No              | No               |

| b0101             | No          | Yes          | No              | Yes              |

| b0110             | No          | Yes          | Yes             | No               |

| b0111             | No          | Yes          | Yes             | Yes              |

| b1000             | Yes         | No           | No              | No               |

| b1001             | Yes         | No           | No              | Yes              |

| b1010             | Yes         | No           | Yes             | No               |

| b1011             | Yes         | No           | Yes             | Yes              |

| b1100             | Yes         | Yes          | No              | No               |

| b1101             | Yes         | Yes          | No              | Yes              |

| b1110             | Yes         | Yes          | Yes             | No               |

| b1111             | Yes         | Yes          | Yes             | Yes              |

a. See *Region Attributes <n> Register* on page 3-20 for programming information.

Table 2-5 shows a typical example of memory map along with the register programming. The TZASC is configured to have 16 regions.

Table 2-5 Typical example of memory map along with the register programming

| Region                | Regiona | Lock | Starting address | Region<br>size | Size<br>field | spb  | Description                                                                                                      |

|-----------------------|---------|------|------------------|----------------|---------------|------|------------------------------------------------------------------------------------------------------------------|

| Region_0<br>(Default) | Enable  | No   | 0×0              | max            | -             | 1100 | Secure Read Write access (RW).                                                                                   |

| Region_1              | Enable  | No   | 0x0              | 64MB           | b011001       | 1111 | Non-secure <i>Read or Write access</i> (R/W), Secure R/W.                                                        |

| Region_2              | Enable  | No   | 0x0              | 16MB           | b010111       | 1110 | Non-secure <i>Read Only access</i> (RO), Secure RW for the normal world OS kernel.                               |

| Region_3              | Enable  | No   | 0x3D00000        | 512KB          | b010010       | 1111 | Regularly switched Non-secure, or Secure RW for a more complex shared memory buffers.                            |

| Region_4              | Enable  | No   | 0x3D80000        | 512KB          | b010010       | 1100 | Non-secure <i>No Access</i> (NA), Secure RW, a dedicated area for secure LCD Controller frame buffer.            |

| Region_5c             | Enable  | No   | 0×80000000       | 32KB           | b001110       | 1111 | Non-secure RW, Secure RW for address range of general peripherals such as screen control, and keyboard hardware. |

| Region_6              | Enable  | Yes  | 0x3C00000        | 512KB          | b010010       | 1011 | Non-secure RW, Secure RO for streaming from the normal world to the secure world.                                |

| Region_7              | Enable  | Yes  | 0x3C80000        | 512KB          | b010010       | 1110 | Non-secure RO, Secure RW for streaming from the secure world to the normal world.                                |

Table 2-5 Typical example of memory map along with the register programming (continued)

| Region     | Regiona | Lock | Starting address | Region<br>size | Size<br>field | spb  | Description                                                                                                                                       |

|------------|---------|------|------------------|----------------|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Region_8   | Enable  | Yes  | 0x3E00000        | 512KB          | b010010       | 1000 | Non-secure NA, Secure RO for the secure world OS kernel.                                                                                          |

| Region_9   | Enable  | Yes  | 0x3E80000        | 512KB          | b010010       | 1100 | Non-secure NA, Secure RW for the secure world OS applications, heap, and stacks.                                                                  |

| Region_10  | Enable  | Yes  | 0x3F00000        | 1MB            | b010011       | 1100 | Non-secure NA, Secure RW for Secure world OS applications, heap, and stacks.                                                                      |

| Region_11c | Enable  | Yes  | 0×80008000       | 32KB           | b001110       | 1100 | Non-secure NA, Secure RW for address range of secure peripherals such as <i>Random Number Generator</i> (RNG), and cryptography support hardware. |

| Region_12  | Enable  | Yes  | 0xF0000000       | 256MB          | b011011       | 0011 | Non-secure RW, Secure NA for FLASH holding normal world OS plus disk.                                                                             |

| Region_13  | Enable  | Yes  | 0xF0000000       | 1MB            | b010011       | 1100 | Non-secure NA, Secure RW for FLASH for secure boot, secure world OS, secure configuration details.                                                |

| Region_14  | Disable | -    | -                | -              | -             | -    | -                                                                                                                                                 |

| Region_15  | Disable | -    | -                | -              | -             | -    | -                                                                                                                                                 |

a. Region can be either Enable or Disable.

| —— Note                          |                                                             |

|----------------------------------|-------------------------------------------------------------|

| The implementers system design,  | , and security requirements are taken into account for this |

| example. And any actual software | e programming must depend on the system where TZASC is      |

| plugged.                         |                                                             |

#### 2.2.6 **Denied AXI transactions**

If an AXI transaction has insufficient security privileges then for:

Reads

The TZASC responds to the master by setting all bits of the read data bus, rdatas[AXI DATA MSB:0], to zero.

—— Note ———

If the TZASC is programmed to perform speculative accesses, it discards the data that it receives on rdatam[AXI DATA MSB:0].

Writes

The TZASC prevents the transfer of data from the master to the slave by discarding the data that wdatas[AXI DATA MSB:0] contains. If you program the TZASC to perform speculative accesses, it modifies the transfer to the slave by setting all bits of the:

- write data bus, wdatam[AXI DATA MSB:0], to zero

- write data strobe, wstrbm[AXI STRB MSB:0], to zero.

b. Security Permission (sp).

c. In a more typical system, these devices would be protected by a TrustZone Protection Controller (BP147), and associated TrustZone aware AXI to APB Bridges (BP135).

| Note                                                                                                                                                                                         |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| The action Register controls whether the TZASC signals to the master when region permission failure occurs, and if so, the type of response it provides. <i>Action Register</i> on page 3-8. |  |

#### 2.2.7 Speculative accesses

By default, the TZASC performs read or write speculative accesses that means it forwards an AXI transaction address to a slave, before it verifies that the AXI transaction is permitted to read address or write address respectively.

The TZASC only permits the transfer of data between its AXI bus interfaces, after verifying the access that the read or write access is permitted respectively. If the verification fails, then it prevents the transfer of data between the master and slave as *Denied AXI transactions* on page 2-11 describes.

You can disable speculative accesses by programming the speculation\_control Register. See *Speculation Control Register* on page 3-16. When speculative accesses are disabled, the TZASC verifies the permissions of the access before it forwards the access to the slave. If the TZASC:

- Permits the access, it commences an AXI transaction to the slave, and it adds one clock latency.

- Denies the access, it prevents the transfer of data between the master and slave as *Denied AXI transactions* on page 2-11 describes. In this situation, the slave is unaware when the TZASC prevents the master from accessing the slave.

| Note                                                                                                                                                                                                |                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Enabling speculative access is a potential security risk, if the dreacts to this transaction. Most devices do not have to react to speculative access is much faster than validating the address be | this level of access, and |

#### 2.2.8 Preventing writes to registers and using secure\_boot\_lock

By suitably programming lockdown Register, see *Lockdown Select Register* on page 3-9, and asserting **secure\_boot\_lock** signal makes the following registers read only:

- speculation control Register. See *Speculation Control Register* on page 3-16.

- security\_inversion\_en Register. See Security Inversion Enable Register on page 3-17.

- lockdown range Register. See *Lockdown Range Register* on page 3-9.

#### Locking down the region using lockdown\_range and lockdown\_select registers

By programming the lockdown\_select, and lockdown\_range registers, and asserting the **secure\_boot\_lock** signal, you can lockdown the behavior of the TZASC so that it prevents unintentional or erroneous write to the regions specified in the lockdown\_range Register. However, read access to those regions is permitted:

- region setup low <n> Register. See Region Setup Low <n> Register on page 3-18

- region setup high <n> Register. See Region Setup High <n> Register on page 3-19

- region attributes <n> Register. See Region Attributes <n> Register on page 3-20.

The TZASC expects the **secure\_boot\_lock** signal to be asserted for at least one clock cycle. One clock after the **secure\_boot\_lock** is sampled HIGH by TZASC, then the registers mentioned in *Locking down the region using lockdown\_range and lockdown\_select registers* on page 2-12 cannot be written, unless the TZASC is reset by asserting **aresetn**.

#### 2.2.9 Using locked transaction sequences

If a master performs locked transaction sequences, a transaction might stall, or an AXI protocol violation might occur when:

#### Transaction sequence crosses a 4KB boundary

If a locked transaction sequence crosses a 4KB boundary and the regions have different region permissions, the TZASC might prevent access to the second region and therefore the slave would not receive the latter part of the locked transaction sequence.

| Note                                                                                       |           |

|--------------------------------------------------------------------------------------------|-----------|

| The AXI protocol recommends that locked transaction sequences do not 4KB address boundary. | t cross a |

#### Secure state change

During a locked transaction sequence, if a master changes the state of **arprots[1]** or **awprots[1]** and the region has different region permissions for Secure state and Non-secure state, the TZASC might deny a transaction and therefore the slave would not receive the latter part of the locked transaction sequence.

#### Reads and writes

During a locked transaction sequence, if a master performs reads and writes to a region, depending on the region permissions, the TZASC might deny a transaction and therefore the slave would not receive the latter part of the locked transaction sequence.

#### 2.2.10 Using exclusive accesses

If a master performs exclusive accesses to an address region, you must program the TZASC to permit read and write accesses to that address region, for the expected settings of **arprots[1]** and **awprots[1]**, otherwise the read or write transaction might fail.

#### 2.3 Constraints of use

The TZASC has the following considerations relating to change in programmers view on an active system:

- When changing the setting of a TZASC region,

- The current accepted AXI transaction, if it falls into that region, would act according to the previous settings for that region.

- Any other outstanding AXI transactions, that falls into that region, would effect by the new settings for that region.

- Given little ability to predict that the mentioned AXI transactions would effect, it is obviously desirable that there are no outstanding AXI transactions when a regions setting are changed.

- In simple systems this can potentially be achieved by the core not accessing the given region during the period of the cores transition between security states. Even in these cases, the status of cached data and instructions needs to be considered.

- In more complicated systems the code that changes the TZASC region settings must have to inform other AXI bus masters to desist or complete acting on that region before performing the region setting changes. After having such an action acknowledged the code must also have to instigate a suitable delay before then acting.

An example of this can be an LCD controller dealing with a frame buffer that is switching between a Normal world and Secure world use.

| Note ———                                                                                       |

|------------------------------------------------------------------------------------------------|

| There is no direct mechanism to ascertain if there are any outstanding AXI transactions, and s |

| the designer must use their system knowledge to apply reasonable mechanisms.                   |

It is recommended that any DECERR, or TZASC interrupt handler is designed to expect, and potentially ignore events generated under these circumstances.

## Chapter 3 **Programmers Model**

This chapter describes the TZASC registers, and provides information for programming the device. It contains the following sections:

- *About the programmers model* on page 3-2

- Register descriptions on page 3-5.

#### 3.1 About the programmers model

The following information applies to the TZASC registers:

- The base address of the TZASC is not fixed, and can be different for any particular system implementation. The offset of each register from the base address is fixed.

- Do not attempt to access reserved or unused address locations. Attempting to access these location can result in Unpredictable behavior of the TZASC.

- Unless otherwise stated in the accompanying text:

- do not modify undefined register bits

- ignore undefined register bits on reads

- all register bits are reset to a logic 0 by a system or power-on reset.

- For programming the registers, the TZASC supports data in word-invariant endianness.

- The Type column in Table 3-1 on page 3-5 describes the access types as follows:

- **RW** Read and write.

- **RO** Read only.

- **WO** Write only.

- System designers must ensure that only processors in Secure state can access the registers, otherwise it can compromise the security of the system.

| Note                                                                                      |   |

|-------------------------------------------------------------------------------------------|---|

| See Constraints of use on page 2-14 for more information about considerations relating to | ) |

| change in programmers view on an active system.                                           |   |

#### 3.1.1 Register map

The register map of the TZASC spans a 4KB region, as Figure 3-1 shows.

Figure 3-1 Register map

In Figure 3-1, the register map consists of the following regions:

#### Configuration, lockdown, and interrupt

Use these registers to determine the global configuration of the TZASC, and control its operating state.

**Fail status** These registers provide information about an access that failed because of insufficient permissions.

**Control** Use these registers to enable the TZASC to perform security inversion or speculative accesses.

#### **Region control**

Use these registers to control the operating state of each region.

#### **Integration test**

Use these registers when testing the integration of the TZASC in a *System-on-Chip* (SoC). See Chapter 4 *Programmers Model for Test* for more information.

#### **Component configuration**

These registers enable the identification of system components by software.

# 3.2 Register descriptions

This section describes the registers that the TZASC provides. Table 3-1 lists the registers.

**Table 3-1 Register summary**

| configuration action ockdown_range ockdown_select nt_status nt_clear cail_address_low cail_address_high cail_control | RO RW RWb RWc RO WO - RO RO                                                   | -a 0x00000001 0x00000000 0x00000000 0x00000000              | 32<br>32<br>32<br>32<br>2<br>32<br>-<br>32                                                                       | Configuration Register on page 3-6  Action Register on page 3-8  Lockdown Range Register on page 3-9  Lockdown Select Register on page 3-9  Interrupt Status Register on page 3-11  Interrupt Clear Register on page 3-12  Reserved  Fail Address Low Register on page 3-12 |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ockdown_range ockdown_select nt_status nt_clear ail_address_low ail_address_high ail_control                         | RWb<br>RWc<br>RO<br>WO<br>-<br>RO                                             | 0x00000000<br>0x00000000<br>0x00000000<br>0x000000          | 32<br>32<br>2<br>32<br>-                                                                                         | Lockdown Range Register on page 3-9  Lockdown Select Register on page 3-9  Interrupt Status Register on page 3-11  Interrupt Clear Register on page 3-12  Reserved                                                                                                          |

| ockdown_select  nt_status  nt_clear  ail_address_low ail_address_high ail_control                                    | RW° RO WO - RO RO                                                             | 0x00000000<br>0x000000000<br>0x000000000<br>-<br>0x00000000 | 32<br>2<br>32<br>-                                                                                               | Lockdown Select Register on page 3-9  Interrupt Status Register on page 3-11  Interrupt Clear Register on page 3-12  Reserved                                                                                                                                               |

| nt_status nt_clear  ail_address_low ail_address_high ail_control                                                     | RO<br>WO<br>-<br>RO                                                           | 0x00000000<br>0x000000000<br>-<br>0x00000000                | 2 32 -                                                                                                           | Interrupt Status Register on page 3-11 Interrupt Clear Register on page 3-12 Reserved                                                                                                                                                                                       |

| nt_clear  ail_address_low ail_address_high ail_control                                                               | WO - RO RO                                                                    | 0x00000000<br>-<br>0x00000000                               | 32                                                                                                               | Interrupt Clear Register on page 3-12 Reserved                                                                                                                                                                                                                              |

| ail_address_low ail_address_high ail_control                                                                         | -<br>RO<br>RO                                                                 | -<br>0×000000000                                            | -                                                                                                                | Reserved                                                                                                                                                                                                                                                                    |

| ail_address_high                                                                                                     | RO                                                                            |                                                             |                                                                                                                  |                                                                                                                                                                                                                                                                             |

| ail_address_high                                                                                                     | RO                                                                            |                                                             | 32                                                                                                               | Fail Address Low Register on page 3-12                                                                                                                                                                                                                                      |

| ail_control                                                                                                          |                                                                               | 0x00000000                                                  |                                                                                                                  |                                                                                                                                                                                                                                                                             |

| <del></del>                                                                                                          | RO                                                                            |                                                             | 32                                                                                                               | Fail Address High Register on page 3-13                                                                                                                                                                                                                                     |

| ail_id                                                                                                               |                                                                               | 0x00000000                                                  | 32                                                                                                               | Fail Control Register on page 3-14                                                                                                                                                                                                                                          |

|                                                                                                                      | RO                                                                            | 0x00000000                                                  | _d                                                                                                               | Fail ID Register on page 3-15                                                                                                                                                                                                                                               |

| peculation_control                                                                                                   | RWb                                                                           | 0x00000000                                                  | 32                                                                                                               | Speculation Control Register on page 3-16                                                                                                                                                                                                                                   |

| ecurity_inversion_en                                                                                                 | RWb                                                                           | 0×00000000                                                  | 32                                                                                                               | Security Inversion Enable Register on page 3-1                                                                                                                                                                                                                              |

|                                                                                                                      | -                                                                             | -                                                           | -                                                                                                                | Reserved                                                                                                                                                                                                                                                                    |

| region_setup_low_0                                                                                                   |                                                                               |                                                             |                                                                                                                  |                                                                                                                                                                                                                                                                             |

| region_setup_low_1                                                                                                   | o_low_1                                                                       |                                                             |                                                                                                                  |                                                                                                                                                                                                                                                                             |

| egion_setup_low_2f                                                                                                   | <b></b>                                                                       |                                                             | 22                                                                                                               | D                                                                                                                                                                                                                                                                           |

|                                                                                                                      | RWe 0x00000000                                                                |                                                             | 32                                                                                                               | Region Setup Low <n> Register on page 3-18</n>                                                                                                                                                                                                                              |

|                                                                                                                      |                                                                               |                                                             |                                                                                                                  |                                                                                                                                                                                                                                                                             |

| region_setup_low_15f                                                                                                 |                                                                               |                                                             |                                                                                                                  |                                                                                                                                                                                                                                                                             |

| egion_setup_high_0                                                                                                   |                                                                               |                                                             |                                                                                                                  |                                                                                                                                                                                                                                                                             |

| egion_setup_high_1                                                                                                   |                                                                               |                                                             |                                                                                                                  |                                                                                                                                                                                                                                                                             |

| region_setup_high_2f                                                                                                 |                                                                               |                                                             |                                                                                                                  |                                                                                                                                                                                                                                                                             |

|                                                                                                                      | RWe                                                                           | 0x00000000                                                  | 32                                                                                                               | Region Setup High <n> Register on page 3-19</n>                                                                                                                                                                                                                             |

|                                                                                                                      |                                                                               |                                                             |                                                                                                                  |                                                                                                                                                                                                                                                                             |

|                                                                                                                      |                                                                               |                                                             |                                                                                                                  |                                                                                                                                                                                                                                                                             |

|                                                                                                                      | egion_setup_low_15f egion_setup_high_0 egion_setup_high_1 egion_setup_high_2f | egion_setup_low_15f egion_setup_high_0 egion_setup_high_1   | RWe 0x00000000  egion_setup_low_15f  egion_setup_high_0  egion_setup_high_1  egion_setup_high_2f  RWe 0x00000000 | RWe 0x00000000 32  egion_setup_low_15f  egion_setup_high_0 egion_setup_high_1 egion_setup_high_2f  RWe 0x00000000 32                                                                                                                                                        |

**Table 3-1 Register summary (continued)**

| Offset      | Name                             | Type | Reset                                                                          | Width | Description                                     |  |

|-------------|----------------------------------|------|--------------------------------------------------------------------------------|-------|-------------------------------------------------|--|

| 0x108       | region_attributes_0              |      | 0xc0000000                                                                     |       |                                                 |  |

| 0x118       | region_attributes_1              | _    |                                                                                | =     |                                                 |  |

| 0x128       | region_attributes_2f             | _    |                                                                                |       |                                                 |  |

| •           |                                  | - RW | 0x0000001c                                                                     | 32    | Region Attributes <n> Register on page 3-20</n> |  |

| •           | •                                |      |                                                                                |       |                                                 |  |

| 0x1F8       | region_attributes_15 f           |      |                                                                                |       |                                                 |  |

| 0x1nCg      | -                                | -    | -                                                                              | -     | Reserved                                        |  |

| 0x200-0xDFC | -                                | -    | -                                                                              | -     | Reserved                                        |  |

| 0xE00       | itcrg                            |      |                                                                                |       |                                                 |  |

| 0xE04       | itip                             |      | See Chapter 4 Programmers Model for Test for information about these registers |       |                                                 |  |

| 0xE08       | itop                             |      |                                                                                |       |                                                 |  |

| 0xE0C-0xEFC |                                  |      | -                                                                              | -     | Reserved                                        |  |

| 0xFD0       | periph_id_4                      | RO   | 0x00000004                                                                     | 8     | Davish and I dout Gostion Books are as 2.22     |  |

| 0xFE0-0xFEC | periph_id_[3:0] RO 0x000BB380h 8 |      | - Peripheral Identification Registers on page 3-23                             |       |                                                 |  |

| 0xFF0-0xFFC | 0-0xFFC component_id_[3:0]       |      | 0xB105F00D                                                                     | 8     | Component Identification Registers on page 3-25 |  |

- a. The reset value depends on the configuration of the TZASC.

- b. Access type can become RO depending on **secure\_boot\_lock** and the value of the lockdown\_select Register. See *Lockdown Select Register* on page 3-9.

- c. Access type becomes RO if secure\_boot\_lock goes HIGH.

- d. Dependant on configuration, range from 31-0.

- e. Access type is RW for all regions, except region 0 is RO.

- f. The configuration of the TZASC controls the number of regions, and therefore, the region\_<...>\_2 to region\_<...>\_15 registers that are available.

- g. For values of n from 0x0 to 0xF inclusive.

- h. The reset value depends on the revision of the TZASC. See Peripheral Identification Register 2 on page 3-24.

#### 3.2.1 Configuration Register

The configuration Register characteristics are:

**Purpose** Provides information about the configuration of the TZASC.

**Usage constraints** There are no usage constraints.

**Configurations** Available in all configurations of the TZASC.

**Attributes** See the register summary in Table 3-1 on page 3-5.

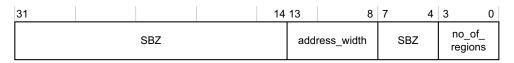

Figure 3-2 shows the configuration Register bit assignments.

Figure 3-2 configuration Register bit assignments

Table 3-2 shows the configuration Register bit assignments.

Table 3-2 configuration Register bit assignments

| Bits    | Name          | Function                                                                                                                                                  |

|---------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:14] | -             | Reserved, Should be Zero (SBZ).                                                                                                                           |

| [13:8]  | address_width | Returns the width of the AXI address bus. Read as: b0000000-b011110 = reserved b011111 = 32-bit b100000 = 33-bit b100001 = 34-bit                         |

| [7:4]   | -             | Reserved, SBZ.                                                                                                                                            |

| [3:0]   | no_of_regions | Returns the number of regions that the TZASC provides:  b0000 = reserved  b0001 = 2 regions  b0010 = 3 regions  b0011 = 4 regions  .  b1111 = 16 regions. |

# 3.2.2 Action Register

The action Register characteristics are:

**Purpose** Controls the response signaling behavior of the TZASC to region

permission failures.